System Interrupts (OCR A Level Computer Science): Revision Note

Exam code: H446

System Interrupts

What are interrupts?

In A Level Computer Science, an interrupt is a signal to the processor that stops its current task and performs a different task temporarily

Interrupts can be hardware events or time-sensitive tasks

When an interrupt occurs, the processor suspends the current program execution and transfers control to an interrupt service routine

Purpose and role of interrupts

Real-time Event Handling: hardware errors and signals from input devices e.g. hard disk failure

Device Communication: alerts from external devices e.g. printer jams and network errors

Multitasking: suspending processing in one application so that the user can switch to another

Types of interrupts

Type | Definition | Example |

|---|---|---|

Hardware Interrupts | Generated by external devices | Keyboard input, mouse movements, disk I/O requests |

Software Interrupts | Triggered by software or the operating system | Application requests to open a file, division by zero errors |

Trap Interrupts | Intentionally triggered by a program | Software debugging, handling unexpected error cases |

The interrupt process

Interrupt Request (IRQ)

An external device or software generates an interrupt, signalling the processor to stop its current task

The interrupt controller passes this to the interrupt handler for assessment

Interrupt Acknowledge

The interrupt handler decides if the interrupt needs to be dealt with now or later

If yes, the current contents of the processor registers are saved in memory

Interrupt Service Routine (ISR) Lookup

The processor fetches the corresponding Interrupt Service Routine (ISR) associated with the interrupt type

ISR Execution

The processor transfers control to the ISR and executes the routine to handle the specific interrupt

Interrupt Exit

After the ISR completes, the processor restores the content of the registers from step 2

The fetch-decode-execute cycle is resumed

The interrupt process

What is an ISR?

An ISR is a special function that handles a particular interrupt type

Each type of interrupt has a corresponding routine, e.g. printer jam, hard disk failure, file download error, network connection error all have routines to be followed when they happen

ISRs should be concise, efficient, and carefully designed to minimise the time taken to execute, as they often need to handle time-sensitive events

Interrupt priority and nesting

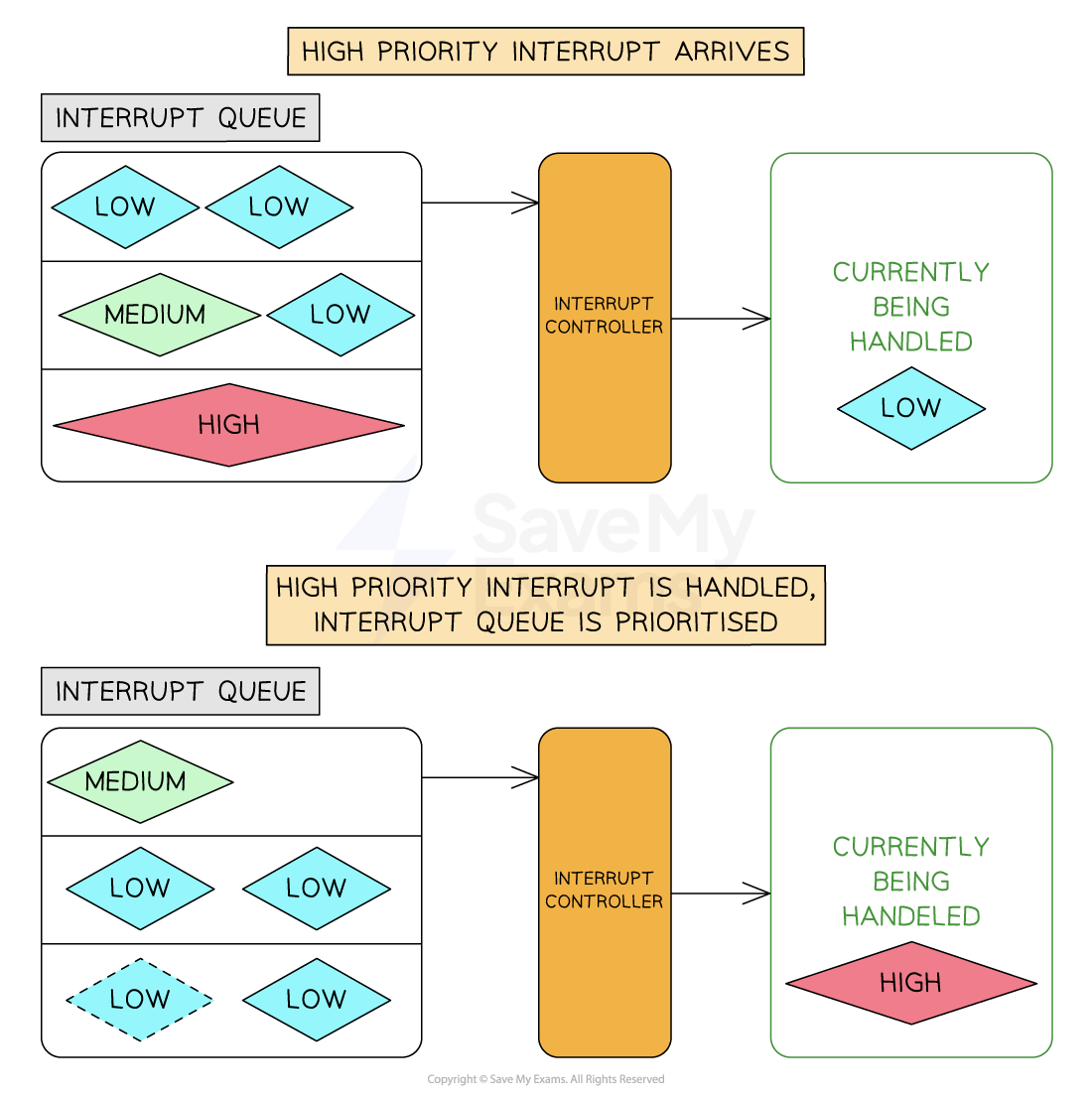

Interrupt prioritisation means the processor can acknowledge and switch to resolving a higher-priority interrupt

Prioritising interrupts is vital because many things can go wrong at the same time

Lower-priority ISRs may be temporarily suspended until the higher-priority ISR completes the execution

Nesting of interrupts refers to the ability of the processor to handle interrupts within interrupts

Proper management of nested interrupts avoids potential conflicts and ensures system stability

Nesting of interrupts

Interrupt priority handling

System handling of interrupt priority

Unlock more, it's free!

Was this revision note helpful?